《Cadence电路板设计入门》周润景,张晨编著|(epub+azw3+mobi+pdf)电子书下载

图书名称:《Cadence电路板设计入门》

- 【作 者】周润景,张晨编著

- 【页 数】 408

- 【出版社】 西安:西安电子科技大学出版社 , 2015.10

- 【ISBN号】978-7-5606-3769-3

- 【价 格】58.00

- 【分 类】印刷电路-计算机辅助设计

- 【参考文献】 周润景,张晨编著. Cadence电路板设计入门. 西安:西安电子科技大学出版社, 2015.10.

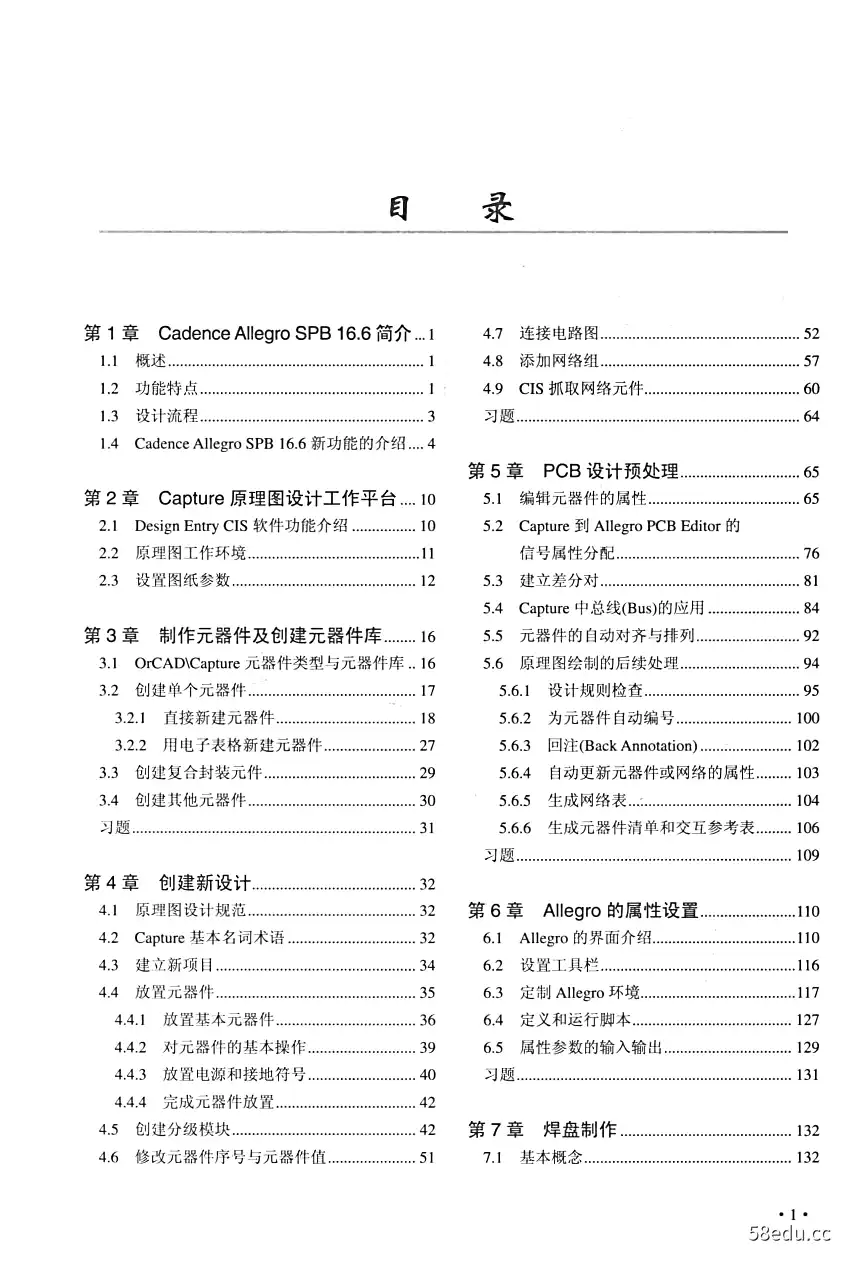

图书目录:

《Cadence电路板设计入门》内容提要:

本书介绍了应用CadenceAllegroSPB16.6软件进行PCB电路板设计的全过程,主要内容包括原理图输入、元器件数据集成管理环境的使用、PCB信号完整性设计基础知识、PCB设计、后期电路设计处理需要掌握的各种技能等。

《Cadence电路板设计入门》内容试读

第1章Cadence Allegro SPB16.6简介

第章

Cadence Allegro SPB16.6简介

1.1概述

Cadence新一代的Allegro SPB 16.6系统互连设计平台优化并加速了高性能、高密度的互连设计的能力,建立了从IC制造、封装到PCB的一整套完整的设计流程.Cadence Allegro

可提供新一代的协同设计方法,以便建立跨越整个设计链,包括/O缓冲区、IC、封装及

PCB设计人员的合作关系。

功能强大的Allegro PCB是业界领先的PCB设计系统。Allegro PCB是一个交互的环境,

用于建立和编辑复杂的多层PCB,其丰富的功能可以满足当今世界设计和制造的需求。针

对按时完成系统协同设计的不同需求,Cadence Allegro平台能协同设计出高性能的集成电

路、封装和PCB的互连,降低成本并加快产品上市时间。

Cadence Allegro系统互连平台能够跨集成电路、封装和PCB协同设计实现高性能互连。

应用平台的协同设计方法,工程师可以迅速优化/O缓冲器,或者跨集成电路、封装和PCB

的系统互连,从而避免硬件设计返工,并降低硬件成本和缩短设计周期。约束驱动的Allegro流程可用于设计捕捉、信号完整性和物理实现。由于得到了Cadence Encounter与Virtuoso平台的支持,Allegro协同设计方法使得高效的设计链协同成为现实。

系统互连是信号的逻辑、物理和电气连接及功率配送的系统。目前,集成电路与系统的设计者在设计高速系统互连时面临着前所未有的挑战:一方面,由于集成电路的集成度

不断增长,芯片的I/O和封装引脚数量也在迅速增加:另一方面,千兆赫兹速度的数据传

输速率导致对极高速的PCB与系统需求增加,同时,PCB尺寸不断缩小,功率配送要求也

随着芯片晶体管数目的蹿升而不断提高。

解决这些复杂的问题和应对不断增长的上市时间压力的需要,使得传统的系统组件设计方法变得过时和不合时宜。在高速系统中完成工作系统互连需要新一代的设计方法,而设计团队应该把注意力集中在提高跨三个系统领域的系统互连的效率上。

1.2功能特点

Cadence公司的Allegro SPB 16.6系统针对PCB板级的电路系统设计流程提供了完整

的输入、分析、版图编辑和制造的全线EDA辅助设计工具,这些辅助设计工具可以完成原

理图输入,数字、模拟及混合电路仿真,FPGA可编程逻辑器件设计,自动布局、布线,PCB

版图及生产制造数据输出,以及针对高速PCB的信号完整性分析与电源完整性分析等。

Cadence电路板设计入门

整个Allegro SPB16.6系统主要分为25个功能模块:

(I)Allegro PCB Planner:一款可为网络和元器件添加约束规则的PCB设计工具。设计

者可以通过热分析,SI、PI工具为元器件和网络添加约束规则。当与设计创作工具同时使

用时,它可以让设计者在设计数据库时描述约束的设计意图。同时该工具还具有布线规划

与PCB数据的编辑、查看能力,可让设计者轻松快速地对不同布局策略的效果做出评估。

(2)Cadence Help:Cadence的帮助工具,对Cadence的各个部分都有详细的讲解。

(3)Design Entry CIS:世界上领先的在Windows操作系统上实现原理图输入的解决方案,直观、简单易用且具有先进的部件搜索机制,可迅速选择设计捕捉工具。Design EntryCIS较以前的Capture和Capture CIS,其设计快捷方便,图形美观,能与Allegro实现无缝链接。

(4)Design Entry HDL Rules Checker:Design Entry HDL的规则检查工具。

(5)Design Entry HDL:提供了一个原理图输入和分析环境。它与扩展模拟(数字电路和

模拟电路)以及PCB版图设计解决方案集成在一起,可作为所有与系统和高速设计流程相

关的满足CAE要求的任务中心。Design Entry HDL可使得设计的每一个阶段流水线化。

(6)FPGA System Planner:也称FPGA系统设计平台,其提供了一套完整的、可扩展

的FPGA-PCB协同式设计解决方案,用于板级FPGA设计。它能够自动对引脚配置进行“芯

片规则算法”的综合优化,取代了易出错的手动引脚配置方式,并以独特的布局解决方案,减少了不必要的设计迭代,可节省创建最优化引脚配置方案的时间,从而提高设计效率。

(T)Library Explorer:管理数字设计库的软件,可以调用Design Entry HDL、PCB

Librarian、PCB Designer、Allegro System Architect等工具建立元器件符号和模型。

(8)License Client Configuration Utility:Cadence证书和证书服务的检查工具。

(9)OrCAD Capture CIS:集成了强大的原理图设计功能,主要特点是具有快捷的元件

信息管理系统(CIS),并具有通用PCB设计入口。其扩展的CIS功能可以方便地访问本地

元件优选数据库和元件信息,并可通过减少重新搜索元器件信息或重复建库、手动输入元件信息、维护元件数据的时间等方法来提高设计效率。

(IO)OrCAD Capture:一款多功能的PCB原理图输入工具。OrCAD Capture提供了完

整的、可调整的原理图设计方法,能够有效地应用于PCB的设计创建、管理和重用。OCAD

Capture与OrCAD PCB Editor的无缝数据连接,可以很容易地实现物理PCB的设计。其与

Cadence PSpice A/D的高度集成,可以实现电路的数模混合信号仿真。

(I1)Package Designer:芯片和封装的设计分析软件。它把芯片级的I/O可行性和规划功能与业界领先的集成电路封装设计工具组合到一起,提供了一种强大的协同设计方法。

该产品家族包括一个嵌入式、经过验证的3D场计算器,允许工程师在电气与物理设计要

求之间做出折中选择,以满足成本和性能目标。

(12)PCB Editor:一个完整的高性能PCB设计软件,通过顶尖的技术,为创建和编辑

复杂、多层、高速、高密度的PCB设计提供了一个交互式、约束驱动的设计环境。它允许用

户在设计过程的任意阶段定义、管理和验证关键的高速信号,并能抓住最关键的设计问题。

(13)PCB Router:CCT布线器。

(14)PCB SI:提供了一个集成的高速设计与分析环境。它能完成高速数字PCB系统和

高级集成电路封装设计,方便电气工程师在设计周期的所有阶段探究、优化和解决与电气性

第1章Cadence Allegro SPB16.6简介

能相关的问题。约束驱动的设计流程提高了首次成功的概率,并降低了产品的整体成本。

(I5)Physical Viewer::.Allegro浏览器模块。

(l6)Project Manager:Cadence的项目管理器,用于Cadence中项目和元件库的交互与管理,提供树形图的交互方式。

(I7)Pspice AD:模拟和数模混合信号仿真器,为用户提供一整套完整的电路仿真、验证解决方案。

(I8)PSpice Advanced Analysis:.PSpice的高级仿真工具,它融合了很多技术,用以改善设计性能,提高成本效益和可靠性。这些技术包括信号灵敏度、多引擎的优化器以及应力分析和蒙特卡罗分析。

(I9)Cadence SiP Digital Architect::利用互连管理与驱动协同设计方法论为设计的早期

探索、评估与权衡提供一个横跨芯片抽象、封装衬底和PCB系统间的SP概念原型环境。

SiP Digital Architect可以为架构工程师提供独特的环境来浏览和定义系统连接关系与功能,使得同步协同设计可以在IC、SiP封装衬底以及目标PCB系统间进行优化。工程人员能进行快速的“假设”可行性研究,以确保最大化的器件功能密度性能,同时使功耗最小化。

它具有交叉结构工程变更单(ECO)和版图原理图对比确认功能,完全支持IC驱动或封装/

电路板衬底驱动的设计流程。

(2O)SIP(System-In-Package):系统级封装的设计工具。

(21)System Architect:复杂高速PCB设计工具,具有传统原理图、HDL语言和电子数据表三种设计输入方式。

(22)AMS Simulator:工业标准的模拟、数字及模拟/数字混合信号仿真系统,具有仿真速度快、精度高、功能强大等特点。其仿真库内所含元器件种类丰富,数量众多。

(23)PCB Editor Utilities::包含Pad Designer、DB Doctor和Batch DRC等工具。(24)PCB SI Utilities:.PCB信号完整性分析实用工具。(25)PSpice Accessories:PSpice相关附件工具。

1.3设计流程

整个PCB的设计流程可分为以下三个主要部分。

1.前处理

前处理是指开始PCB设计前的所有准备工作。具体工作如下:

(I)原理图的设计。设计者根据设计要求用Capture软件绘制电路原理图。

(2)创建网络表。绘制好的原理图经检查无误后,可以生成送往Allegro的网络表。网络表文件包含pstxnet..dat、pstxprt.dat和pstchip.dat。

(3)建立元器件封装库。在创建网络表之前,每个元器件都必须有封装。由于实际元器件的封装是多种多样的,如果元器件的封装库中没有所需的封装,就必须自己动手创建元器件封装,并将其存放在指定目录下。

(4)创建机械设计图。设置PCB外框及高度限制等相关信息,产生新的机械图文件

Mechanical Drawing)并存储到指定目录下。

Cadence电路板设计入门

adence

2.中处理

中处理是整个PCB设计中最重要的工作部分。具体工作如下:

(1)读取原理图的网络表。将创建好的网络表导入Allegro软件,取得元器件的相关信息。

(2)摆放机械图和元器件。先摆放创建好的机械图:其次摆放比较重要的或较大的元

器件,如/O端口器件、集成电路:最后摆放小型的元器件,如电阻、电容等。

(3)设置PCB的层面。对于多层PCB,需要添加PCB的层面,如添加Vcc、Gnd层等。

(4)进行布线(手工布线和自动布线)。手工布线可以考虑到整个PCB的布局,使布线

最优化,但缺点是布线时间较长:自动布线可以使布线速度加快,但会使用较多的过孔。有时自动布线的路径不一定是最佳的,故经常需要把这两种方法结合起来使用。

(⑤)放置测试点。放置测试点的目的是检查该PCB能否正常工作。

3.后处理

后处理是输出PCB的最后工作。具体工作如下:

(1)文字面处理。为了使绘制的电路图清晰易懂,需要对整个电路图的元器件序号进行重新排列,并使用回注(Back Annotation)命令,使修改的元器件序号在原理图中得到更新。

(2)底片处理。设计者必须设定每一张底片是由哪些设计层面组合而成的,再将底片

的内容输出至文件,然后再将这些文件送至PCB生产车间制作PCB。

(3)报表处理。产生该PCB的相关报表,然后将相关信息提供给后续的工作人员。常

用的报表有元器件报表(Bill of Material Report)、元器件坐标报表(Component Location

Report)、网表报表(Net List Report)、测试点报表(Testpin Report)等。

1.4 Cadence Allegro SPB16.6新功能的介绍

1.原理图更改存储标识(Save Function for Design and Library)

在Cadence OrCAD Capture 16.6(以下简称16.6)系统中,每当工程、原理图页、元件等被编辑或更改后,在Project Manager中都会用“*”加以标记,如图1-4-1所示。

dkmo⊙回PaeE1回RRr1

白Fe,Hiecarchy

B☐Design Resources®-☐demol.dsn

\design1.dsn

白-☐Library

色Nibrary1.olb

-D7400

BNC

DG419AK

EPC1064

EPF8282A/LCC

EPF8282A/LCCA

DEPF8282A_LCC

EPF8282A_LCC1

DFCT16245

DTC55B4257

TLC5602A

Library Cache

图1-4-1更改标注

第1章Cadence Allegro SPB16.6简介

2.新的查找功能特性(Find Function)

在16.6系统的查找工具栏中新增加了两个特性,如图1-4-2所示。

>Property Name=Value:特定属性查找。例如查找PCB Footprint属性为dip2的元器件,可输入PCB Footprint=-dip2*。

>Regular Expressions::特定属性表达式查找。选择此项必须选择“Property Name=

Value”。例如查找元器件编号在2到9的电阻和电容,可输入Part Reference=(CIR)2-9]。

Match Case

SelectAll

DeselectAll

Highlight

Regular Expressions

Property Name=Value

图1-4-2查找工具新特性

3.全局分页连接器替换(Global Replace for OffPage)

在“Editer”→“Global Replace”全局替换和查找中增加了分页连接器的替换,如图1-43所示。

Find And Replace

Find wha城

OK

Entie Deaign Curert Page Only

Obiect Type☐Hehc Ports

Hictarct收Pt

□N献Ae时

图1-4-3“分页连接器替换”

4.器件对齐功能(Component Alignment Enhancements)

在16.6系统中提升了器件对齐功能。在“Allegro PCB Design GXL”中打开“demo_placed.brd”,如图l-4-4所示。单击右键选择“Application Mode”→“Placement Edit”,然后框选图中D1~D4,再单击右键选择“Align Components”,元器件如图1-4-5所示对齐排列。“Options”页面如图1-4-6所示。

411011a90t1t101

411

图1-4-4

“demo_placed.brd"

5

Cadence电路板设计入门

E718I1958Eg8日

盖月1月8010171丝89

CVertical

金图海圆华厘传题

Algnmert Edge(Certes

Equal spacing 616600 mals☐□面m陆

图1-4-5“对齐元器件”

图14-6“0 ptions”页面

>Alignment Direction:排列方向。软件会根据元件原有排列自动选择。>Alignment Edge:排列对齐方式。

>Spacing:元件间距。选择“Equal spacing”(等间距)后可通过“+”和“-”来调整元器件间距。

5.更新器件符号(Symbol Instance Refresh)

相信大家在平时使用中都会遇到这样一种情况,在删除某些线段或其他东西时,不小心将Symbol的Ref或丝印层等也删除了。我们以前的做法是:

①在setup里设置好library的路径:

②Place→update symbol。

这种方法是利用已有的1 library来更新板子里的symbol。.在16.6系统中,我们可以非常简单轻松地实现Update symbol。打开板子,可以看到图1-4-7中左边两个器件的丝印框以及Ref都被删除了。

图1-4-7删除了丝印框和“Ref”的器件

在进入“Placement Edit”模式后框选左边两个元件,单击右键选择“Refresh symbolinstance”,如图1-4-8所示,接着可以看到元件被更新了,如图1-4-9所示。

notate

Mirror

Align conpononts

Swap components

Copy

Refresh symbol instance

Unplace conponent

Place replicate create

Place roplicate apply

Add to group

Show Rats

图1-4-8

“Refresh Symbol Instance”选项

···试读结束···

作者:冯小玲

链接:https://www.58edu.cc/article/1523942584186105857.html

文章版权归作者所有,58edu信息发布平台,仅提供信息存储空间服务,接受投稿是出于传递更多信息、供广大网友交流学习之目的。如有侵权。联系站长删除。